Geneve paged memory organization

Mapper

Mapping in the Geneve is organized in portions of 8 KiB. Each such portion is called a page, and a page is identified by a number from 0 to 255. Accordingly, the complete physical address space has a size of 2048 KiB or 2 MiB.

In order to map a part of physical address space into the logical address space, the page number of the desired memory page must be loaded into the mapper. The logical address space has a size of 64 KiB, so we see up to eight pages at the same time. The mapper is available in the logical address space as 8 consecutive byte addresses, each of which determines which page is shown in which address range.

Although a page can be made visible at any 8 KiB logical address range, programs usually make use of absolute addresses, so they are only correctly executable if the page is mapped at the intended logical position. Pages which contain only non-executed data may be used at any location.

| Native mode | TI mode | Logical address range |

|---|---|---|

| F110 | 8000 | 0000 - 1FFF |

| F111 | 8001 | 2000 - 3FFF |

| F112 | 8002 | 4000 - 5FFF |

| F113 | 8003 | 6000 - 7FFF |

| F114 | 8004 | 8000 - 9FFF |

| F115 | 8005 | A000 - BFFF |

| F116 | 8006 | C000 - DFFF |

| F117 | 8007 | E000 - FFFF |

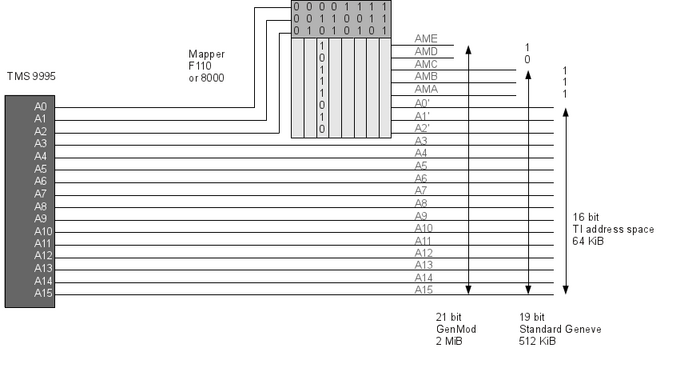

The function of the mapper can be easily understood by this figure.

The mapper contains values to be put on the address lines, selected by A0, A1, and A2 from the processor. As an example, the value 10111010 (>BA) has been loaded into the mapper at location F112. This will cause an access to a card in the Peripheral Box (depending on which card has been selected before) whenever the processor accesses the memory area 4000-5FFF. Below we will give a complete collection of mapping values and associated physical address space.

Right of the mapper we see that in a GenMod configuration, all 21 bits are available in the Peripheral Box. A standard Geneve does not use AMD and AME and can therefore only access 512 KiB in the box. The remaining 1.5 MiB can only be accessed on the Geneve card itself. Only accesses with the first two lines set to 1 and 0 are routed to the box. The essential upgrade within the GenMod is to route all accesses to the box. However, this also means that all cards must decode AMD and AME also. The usual decoding requires AME=1 and AMD=0.

A standard TI only uses the address lines A0-A15 in the Peripheral Box and can only access 64 KiB. All P-Box cards should decode AMA, AMB, and AMC as 1/1/1.

Memory Map

The page numbers are directly related to physical memory locations. Precisely, the complete physical address is created by retrieving the page number indexed by the uppermost three bits of the logical address, adding the 13 bit suffix of the logical address, which in total creates a 21-bit address (16 bits - 3 bits + 8 bits).

The rightmost three bits of the page number are the head of the address, routed over the A0-A2 address lines. The next three bits are called AMA, AMB, and AMC. These lines are available in the Peripheral Expansion Box, but they are not routed through the Flex Cable Interface, so a TI-99/4A console cannot change their value. A Geneve, on the other side, can actually operate these lines. Peripheral Box expansion cards are required to check for AMA=AMB=AMC=1, which is the level that is present for an attached TI. Unfortunately, some third-party cards do not check for this state and cause mirroring of their address space when accessed by a Geneve.

The leftmost two bits of the page number are the (pseudo) address lines AMD and AME, which are not available in the standard P-Box. However, the GenMod Geneve modification grabs two rarely used lines and redefines them as AMD and AME. This way, the complete memory address space can be routed through the P-Box.

| AME | AMD | AMC | AMB | AMA | A0 | A1 | A2 | A3-A15 | pages | size | meaning |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | . | . | . | . | . | . | address | 00..3F | 512 | on-board dram |

| 0 | 1 | . | . | . | . | . | . | address | 40..7F | 512 | on-board future expansion or Memex with Genmod |

| 1 | 0 | 0 | . | . | . | . | . | address | 80..9F | 256 | p-box |

| 1 | 0 | 1 | 0 | . | . | . | . | address | A0..AF | 128 | p-box |

| 1 | 0 | 1 | 1 | 0 | . | . | . | address | B0..B7 | 64 | p-box |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | address | B8 | 8 | Peripheral cards address block 0000-1fff |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | address | B9 | 8 | Peripheral cards address block 2000-3fff |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | address | BA | 8 | Peripheral cards address block 4000-5fff |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | address | BB | 8 | Peripheral cards address block 6000-7fff |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | address | BC | 8 | Peripheral cards address block 8000-9fff |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | address | BD | 8 | Peripheral cards address block a000-bfff |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | address | BE | 8 | Peripheral cards address block c000-dfff |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | address | BF | 8 | Peripheral cards address block e000-ffff |

| 1 | 1 | 0 | . | . | . | . | . | address | C0..DF | 256 | on-board sram expansion |

| 1 | 1 | 1 | 0 | 0 | . | . | . | address | E0..E7 | 64 | on-board sram expansion |

| 1 | 1 | 1 | 0 | 1 | 0 | . | . | address | E8..EB | 32 | on-board sram expansion |

| 1 | 1 | 1 | 0 | 1 | 1 | . | . | address | EC..EF | 32 | on-board sram default |

| 1 | 1 | 1 | 1 | . | . | . | 0 | address | F0,2,4,..,E | 8 | on-board boot eprom 1 |

| 1 | 1 | 1 | 1 | . | . | . | 1 | address | F1,3,5,..,F | 8 | on-board boot eprom 2 |

The TI console (more precisely, the Flex Cable Interface) sets the AMA/B/C

lines to 1. Most cards actually check for AMA/B/C=1. However, this decoding

was forgotten in some designs which cause the card memory to be mirrored. The

usual DSR space at 0x4000-0x5fff which would be reachable via page 0xba is then

mirrored on a number of other pages:

10 xxx 010x = 82, 8a, 92, 9a, a2, aa, b2, ba

Another block to take care of is 0xbc which covers 8000-9fff since this area contains the speech synthesizer port at 9000/9400.

For the standard Geneve, only prefix 10 is routed to the P-Box. The Genmod modification wires these address lines to pins 8 and 9 in the P-Box as AMD and AME. This requires all cards to be equipped with an additional selection logic to detect AMD=0, AME=1. Otherwise these cards, although completely decoding the 19-bit address, would reappear at 512 KiB distances.

For the page numbers we get

standard:

00-3f are internal (DRAM) 40-7f are internal expansion, never used 80-bf are the P-Box address space c0-ff are internal (SRAM, EPROM)

Genmod:

00-3f are the P-Box address space 40-7f are the P-Box address space 80-bf are the P-Box address space c0-ef are the P-Box address space f0-ff are internal (EPROM)